- 您现在的位置:买卖IC网 > Sheet目录1203 > COREPCIF-RM (Microsemi SoC)IP MODULE COREPCIF

�� �

�

�

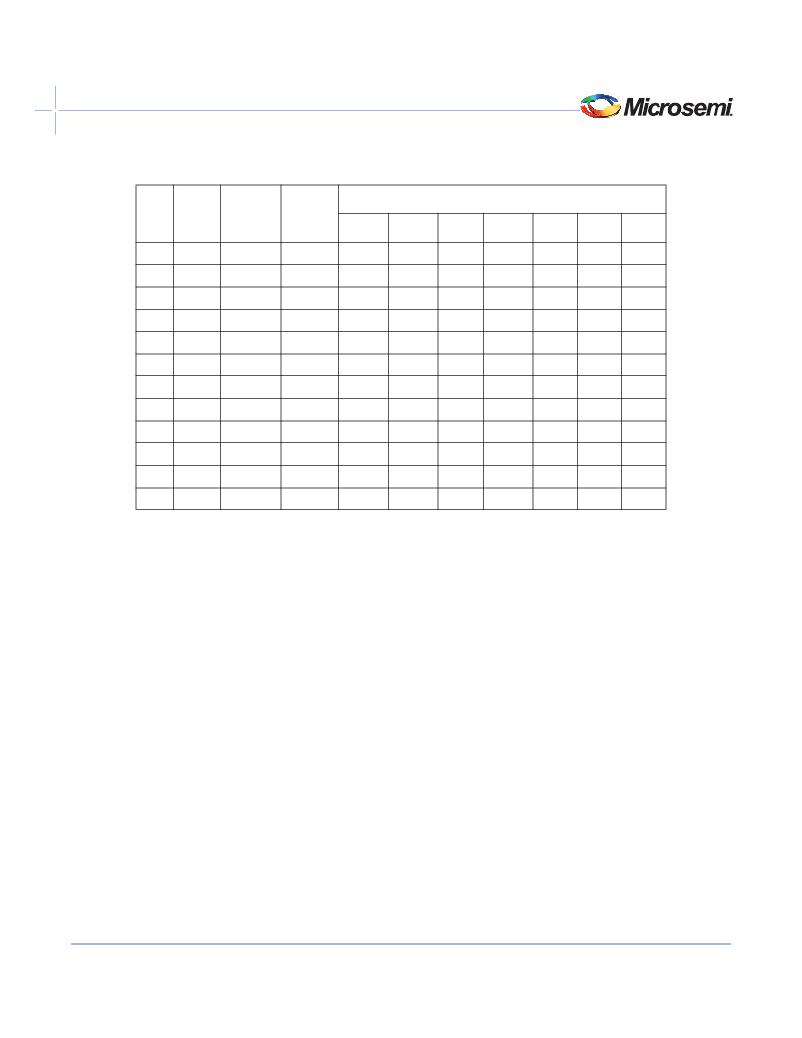

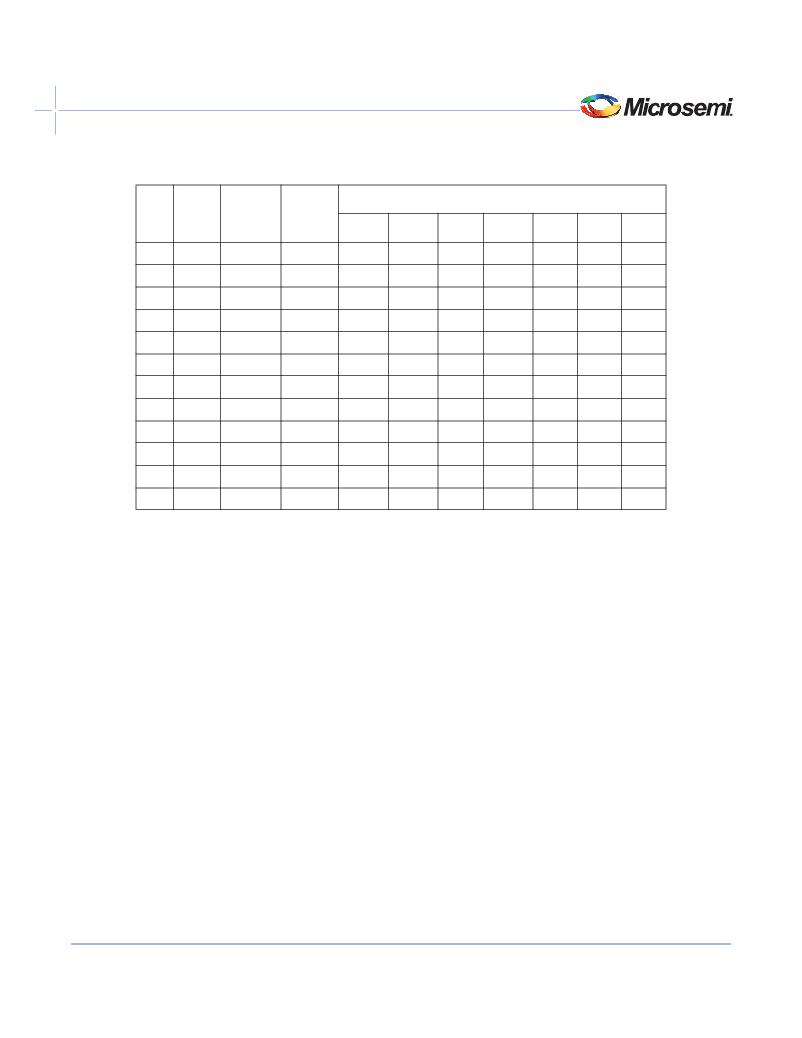

�Table� 7-21� ·� DMA� Control� Register� 5C� Hex� (Continued)�

�Bit(s)� Type�

�Description�

�Cycle� Type�

�Sets� the� DMA� transfer� type� and� direction.� These� four� bits� directly� set� the� PCI� transfer� type.� Any� of� the� sixteen� PCI�

�commands� may� be� used,� but� the� recommended� commands� are� as� follows:�

�0010�

�0011�

�Data� is� moved� from� the� PCI� bus� to� the� backend.�

�An� I/O� Read� command� is� used� on� the� PCI� bus.�

�Data� is� moved� from� the� backend� to� the� PCI� bus.�

�An� I/O� Write� command� is� used� on� the� PCI� bus.�

�7:4�

�RW�

�0110�

�0111�

�1010�

�1011�

�1100�

�Data� is� moved� from� the� PCI� bus� to� the� backend.�

�A� Memory� Read� command� is� used� on� the� PCI� bus.�

�Data� is� moved� from� the� backend� to� the� PCI� bus.�

�A� Memory� Write� command� is� used� on� the� PCI� bus.�

�Data� is� moved� from� the� PCI� bus� to� the� backend.�

�A� Configuration� Read� command� is� used� on� the� PCI� bus.�

�Data� is� moved� from� the� backend� to� the� PCI� bus.�

�A� Configuration� Write� command� is� used� on� the� PCI� bus.�

�Data� is� moved� from� the� PCI� bus� to� the� backend.�

�A� Memory� Read� Multiple� command� is� used� on� the� PCI� bus.�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�23:16�

�25:24�

�114�

�RW�

�RW�

�W�

�RO�

�RW�

�RW�

�RW�

�RW�

�RW�

�RO�

�DMA� Enable�

�This� bit� must� be� set� to� 1� to� enable� any� DMA� transfers.�

�Transfer� Width�

�Writing� a� '1'� to� this� bit� enables� a� 64-bit� memory� transaction.� For� 32-bit� cores,� this� bit� is� read-only� and� is� set� to� 0.�

�Flush� Internal� FIFOs�

�Only� has� an� effect� when� the� FIFO� recovery� logic� is� enabled.� When� written� with� a� '1',� all� internal� FIFOs� will� be�

�flushed.� When� the� FIFOs� are� flushed,� any� data� that� was� stored� in� them� will� be� lost.� Always� returns� 0� when� read.�

�Reserved.� Returns� 0.�

�DMA� Interrupt� Status�

�A� '1'� in� this� bit� indicates� that� the� DMA� cycle� has� completed� and� the� interrupt� is� active.� It� is� cleared� by� writing� a� '1'� to�

�this� bit.� Set� to� 0� after� reset.�

�DMA� Interrupt� Enable�

�Writing� a� '1'� to� this� bit� enables� the� DMA� Complete� interrupt.� Set� to� 0� after� reset.�

�Backend� Interrupt� Status�

�A� '1'� in� this� bit� indicates� an� active� backend� interrupt� condition� (backend� assertion� of� EXT_INTn).� It� is� cleared� by�

�writing� a� '1'� to� this� bit.� Set� to� 0� after� reset.� This� bit� can� only� be� set� when� the� backend� interrupt� is� enabled� (bit� 15).�

�Backend� Interrupt� Enable�

�Writing� a� '1'� to� this� bit� enables� the� backend� interrupt.� Writing� a� '0'� to� this� bit� disables� backend� interrupt� support.�

�Byte� Enables�

�These� eight� bits� directly� set� the� byte� enable� values� that� will� be� used� during� the� DMA� transfer.� When� bit� 16� is� 0,�

�CBEN[0]� will� be� active� (LOW).� Bit� 17� controls� CBEN[1],� etc.� In� 32-bit� cores,� bits� 23:20� are� read-only� and� return� 0.�

�For� normal� burst� DMA� transfers,� these� bits� should� be� set� to� 0.�

�Reserved.� Set� to� 0.�

�v4.0�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

相关代理商/技术参数

COREPCIF-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREPCIF-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREPCI-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPRO LEDBULB 10.5-60W B

制造商:Philips Lumileds 功能描述:

COREPRO LEDBULB 10.5-60W E

制造商:Philips Lumileds 功能描述: